👋 Hi there, I'm

Bharadhwaj K

I build |

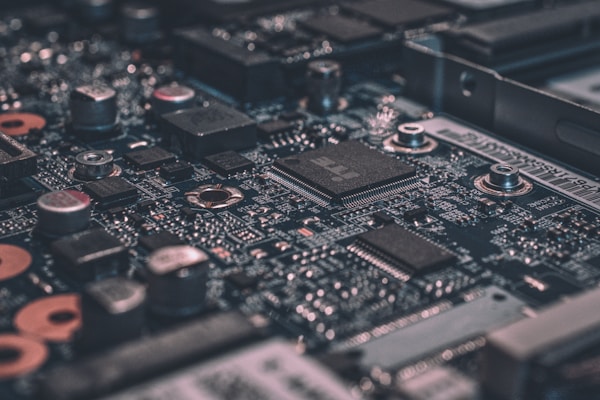

Backend Developer building scalable systems and real-time applications. Experienced with distributed architectures, REST APIs, and RISC-V tooling.

class Engineer:

def __init__(self):

self.name = "Bharadhwaj"

self.role = "Backend Engineer"

self.backend = [

"Node.js",

"Rails"

]

self.systems = [

"RISC-V",

"Distributed"

]